Кафедра биомедицинской инженерии

## Архитектура компьютеров

Учебно-методическое пособие для вузов

## Содержание

| 2 Семействопроцессоров Intel x86.                               | 36 |

|-----------------------------------------------------------------|----|

| 2.1 Микроархитектурапроцессоров 8086 и Pentium Pro              | 37 |

| 2.2 Системакомандиметодыадресациипроцессоров 8086/8088          | 39 |

| 2.2.1 Основныехарактеристикимикропроцессора 8086                | 39 |

| 2.2.2 Регистрыпроцессора                                        | 39 |

| 2.2.3 Организацияпамяти                                         | 42 |

| 2.2.4 Форматыкоманд                                             | 43 |

| 2.2.5 Методыадресации                                           | 46 |

| 2.2.6 Системакоманд                                             | 51 |

| 2.2.7 Математическийсопроцессор                                 | 63 |

| 2.2.8 Организацияввода-вывода                                   | 68 |

| 2.2.9 Организацияпрерываний                                     | 70 |

| 2.2.10 Базоваясистемаввода-вывода BIOS                          | 72 |

| 2.3 32-Разрядныепроцессоры                                      | 74 |

| Приложения                                                      | 80 |

| 1. Списоккомандпроцессораучебной ЭВМ (подмножествосистемыкоманд |    |

| PDP-11)                                                         | 80 |

| 2. Списоккомандпроцессора і8086 (валфавитномпорядке)            | 82 |

| Литература                                                      | 85 |

## 2 Семейство процессоров Intel x86

Первым представителем семейства Intel x86, или, согласно официальной классификации фирмы Intel (Integrated Electronics, США), семейства процессоров IA (Intel Architecture), является микропроцессор 8086, разработанный к 1978 году. Программы, написанные для него, выполняются на всех последующих процессорах семейства, включая все современные модели. Предшествующие процессоры - 8080, 8085 и 4004 (разработка 1967 г.) из-за несовместимости по объектному коду, остаются вне семейства, являясь, тем не менее, важными этапами на пути развития Intel x86 [3]. Сегодня процессоры этого семейства стали стандартом де-факто для большинства персональных компьютеров (ПК) во всем мире. Ниже приводятся основные данные наиболее известных представителей этой серии:

Таблица 1

|                        |                          |                                               |                                |                                  |                               |                                                    | таолица т              |

|------------------------|--------------------------|-----------------------------------------------|--------------------------------|----------------------------------|-------------------------------|----------------------------------------------------|------------------------|

| Название               | Начало произ-<br>водства | Макс. тактовая частота первых серийных образ- | Число<br>транзисторов,<br>млн. | Размер основных<br>регистров ЦПУ | Ширина внешней<br>шины данных | Размер внешнего адресного про-<br>странства памяти | Кэш-<br>память         |

| 8086                   | 1978                     | 8 МГц                                         | 0.029                          | 16                               | 16                            | 1 Мб                                               | нет                    |

| 80286                  | 1982                     | 12.5МГц                                       | 0.134                          | 16                               | 16                            | 16 Мб                                              | 6В на CP <sup>1</sup>  |

| 80386                  | 1985                     | 20 МГц                                        | 0.275                          | 32                               | 32                            | 4 Гб                                               | 8В на CP <sup>1</sup>  |

| 80486                  | 1989                     | 25 МГц                                        | 1.2                            | 32                               | 32                            | 4 Гб                                               | 8KB L1                 |

| Pentium                | 1993                     | 60 МГц                                        | 3.1                            | 32                               | 64                            | 4 Гб                                               | 16KB L1                |

| Pentium<br>Pro (P6)    | 1995                     | 200 МГц                                       | 5.5                            | 32                               | 64                            | 64 Гб                                              | 16 KB L1,<br>256KB L2  |

| Pentium III<br>(P6)    | 1999                     | 1 ГГц                                         | 9.5                            | 32                               | 64                            | 64 Гб                                              | 2x16K L1,<br>512KB L2  |

| Pentium 4              | 2000                     | 1.4 ГГц                                       | 42                             | 32                               | 2x6<br>4                      | 64 Гб                                              | 8K+12K L1,<br>256KB L2 |

| семейство<br>Itanium 1 | 2001                     | 733МГц                                        | 25                             | 64                               | 64                            | 2 <sup>63</sup> +2 <sup>63</sup>                   | 16Ki+16KB<br>L1, 96KB- |

| семейство<br>Itanium 2 | 2002                     | 900МГц                                        | 220-<br>1720                   | 64                               | 128                           | bytes                                              | 2.5MB L2,<br>2-32MB L3 |

Примечание 1: СР - сегментный регистр.

### 2.1 Микроархитектура процессоров 8086 и Pentium Pro

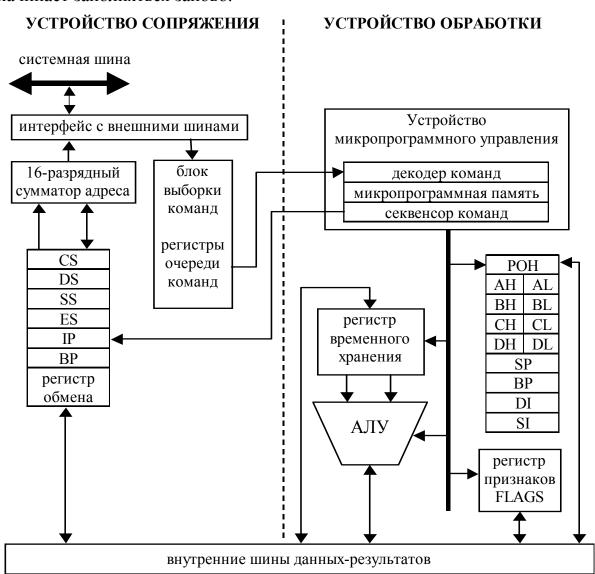

Микропроцессор 8086 ориентирован на выполнение команд параллельно с их выборкой и может быть условно разделен на две части, работающие асинхронно (

Рис. 2.1): устройство сопряжения с внешними шинами (УС) и устройство обработки (УО). Устройство сопряжения обеспечивает формирование 20-разрядного физического адреса памяти, выборку команд и операндов из памяти, организацию очередности команд и запоминание результатов выполнения команд в памяти. В состав УС входит шесть 8-разрядных регистров очереди команд, четыре 16-разрядных сегментных регистра, 16-разрядный регистр обмена и 16-разрядный сумматор адреса, интерфейс с внешними шинами. Регистры очереди команд организованы по принципу FIFO - «первым пришел - первым вышел». УС готово выполнить цикл выборки 16-разрядного слова из памяти всякий раз, когда в очереди освобождаются, по меньшей мере, два байта, а УО извлекает из очереди команды по мере их выполнения. При выполнении команд передачи управления, например условных и безусловных переходов, очередь очищается УС и начинает заполняться заново.

### Рис. 2.1. Микроархитектура процессора 8086

Устройство обработки предназначено для выполнения операций по обработке данных и состоит из устройства микропрограммного управления (УМУ), 16-разрядного АЛУ, восьми 16-разрядных регистров общего назначения и регистра признаков. Команды из очереди, сформированной УС, поступают в УМУ, где декодируются и выполняются в 16-разрядном АЛУ согласно процедурам, записанным в памяти микропрограмм. Последовательное выполнение команд обеспечивается секвенсором команд, часть которого (регистр счетчика команд IP) изображена в составе УС, т.к. именно УС записывает в IP смещение следующей команды, т.е. положение новой команды относительно начала сегмента команд. УО обменивается данными с УС через внутреннюю 16-разрядную шину и регистр обмена (Рис. 2.1).

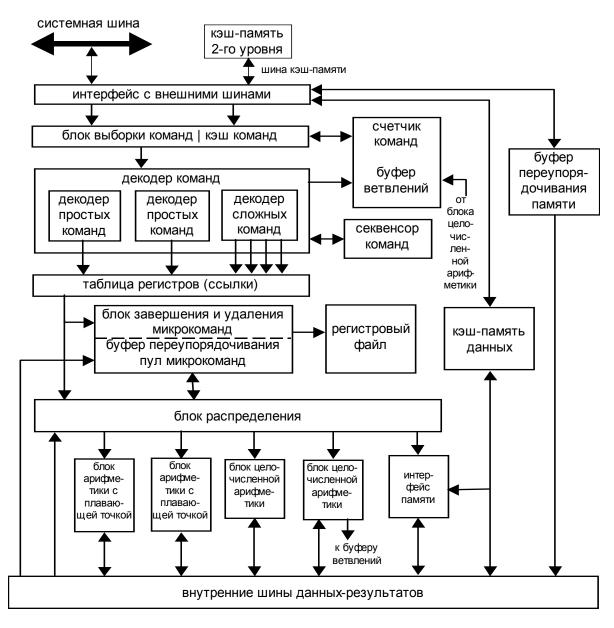

Рис. 2.2. Микроархитектура процессоров семейства Pentium Pro Для сравнения приводится (Рис. 2.2) микроархитектура процессоров

шестого поколения Pentium Pro. Как видно, архитектура со времени 8086 претерпела не только количественные (разрядность внутренних и внешних шин данных, регистров), но и существенные качественные изменения. Pentium Pro имеет суперскалярную архитектуру, т.е. может одновременно выполнять несколько команд за один такт. Эту возможность обеспечивают несколько АЛУ - два блока целочисленной арифметики и два блока с плавающей точкой. Другая важная особенность — т.н. динамическое исполнение — команды разбиваются на простейшие операции, порядок независимого исполнения которых определяется блоком «завершения и удаления микрокоманд» с буферами переупорядочивания и пулом микрокоманд (Рис. 2.2).

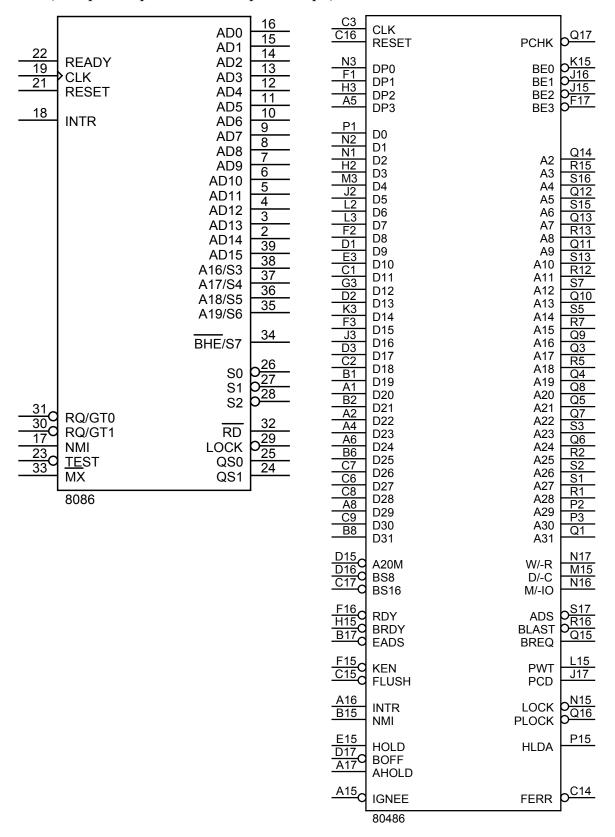

На Рис. 2.3 представлены обозначения микропроцессоров для принципиальных электрических схем, на которых видны внешние шины и сигналы 16-разрядного 8086 и 32-разрядного 80486.

# 2.2 Система команд и методы адресации процессоров 8086/8088

Процессоры 8086/8088 — первые в семействе x86, отличаются друг от друга шириной шины данных: в 8088 — 8-разрядная шина, в 8086 — 16-разрядная. Поэтому чтение и запись 16-разрядных данных выполняются примерно в два раза медленнее для 8088, т.к. возможна передача только одного байта за один цикл, а не 16-разрядного слова как у 8086.

## 2.2.1 Основные характеристики микропроцессора 8086

| Система команд                        | 135 команд                     |

|---------------------------------------|--------------------------------|

| Адресация                             | безадресная, одно-, двухадрес- |

|                                       | ная                            |

| Типы обрабатываемых данных            | биты, байты, 16-разрядные      |

|                                       | слова, строки до 64К байт      |

| Число программно доступных регист-    | 14 шестнадцатиразрядных        |

| ров                                   |                                |

| Число адресуемых устройств вво-       | 64K/64K                        |

| да/вывода                             |                                |

| Число способов вычисления адреса опе- | 24                             |

| рандов памяти                         |                                |

| Разрядность шин адреса/данных         | 20/16                          |

| Объем адресуемой памяти               | 1Мбайт                         |

| Тактовая частота (на момент выпуска)  | 8 МГц                          |

| Максимальное быстродействие (опера-   | 4 млн.                         |

| ции/с типа "регистр-регистр")         |                                |

| Потребляемая мощность                 | не более 1,75 Вт               |

## 2.2.2 Регистры процессора

Микропроцессор 8086 имеет 12 программно-доступных шестнадцатираз-

### рядных регистров (

Рис. 2.1), регистр счетчика команд IP (Instruction Pointer) и регистр флагов (или регистр состояния процессора) FLAGS.

Рис. 2.3 ИС процессоров 8086 и 80486 в DIP и PGA корпусах

Среди программно-доступных регистров выделяют следующие группы (см. Рис. 2.4):

- Регистры данных: AX аккумулятор (Accumulator); BX базовый регистр (Base); CX регистр счетчика (Counter); DX регистр данных (Data).

- Регистры-указатели (индексные регистры): SI индекс источника (Source Index); DI индекс приемника (Destination Index); BP указатель базы (Base Pointer); SP указатель стека (Stack Pointer).

- Сегментные регистры: SS сегмент стека (Stack Segment); DS сегмент данных (Data Segment); ES дополнительный сегмент (Extended data Segment); CS сегмент кода (Code Segment).

16-битные регистры AX, BX, CX, DX состоят из двух 8-битных половин, к которым можно независимо обращаться по именам AH, BH, CH, DH - старшие байты и AL, BL, CL, DL - младшие байты.

|                  | регистры данных |          |    |           |                 |   |  |

|------------------|-----------------|----------|----|-----------|-----------------|---|--|

|                  | 15 8            | 7 0      |    |           | <b>ры</b><br>15 | 0 |  |

| аккумулятор      | AH              | AL       | AX | кода      | CS              |   |  |

|                  |                 |          |    |           |                 |   |  |

| базовый          | ВН              | BL       | вх | данных    | DS              |   |  |

|                  | T               |          | -  |           |                 |   |  |

| счетчик          | СН              | CL       | CX | стека     | SS              |   |  |

|                  | Т               |          | 7  |           |                 |   |  |

| данных           | DH              | DL       | DX | доп.      | ES              |   |  |

|                  |                 |          |    | данных    |                 |   |  |

|                  | адресные        | регистры | _  |           |                 |   |  |

| указатель стека  | ٤               | SP       |    |           |                 |   |  |

|                  |                 |          | _  | указатель | IP              |   |  |

| указатель базы   | BP              |          |    | команд    |                 |   |  |

|                  |                 |          | _  |           |                 |   |  |

| индекс назначе-  | _               | )I       |    | регистр   | FLAG            | s |  |

| пин              |                 |          |    |           |                 |   |  |

|                  |                 |          | 7  | состояния |                 |   |  |

| индекс источника |                 | SI       |    |           |                 |   |  |

Рис. 2.4 Регистры процессора 8086

Биты (или флаги) регистра признаков FLAGS разделяются на условные, отражающие результат предыдущей операции ALU, и управляющие, от которых зависит выполнение специальных функций.

| 15 | 14 | 13 | 12 | 11 | 10 | 09 | 08 | 07 | 06 | 05 | 04 | 03 | 02 | 01 | 00 |

|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

|    |    |    |    | OF | DF | IF | TF | SF | ZF |    | AF |    | PF |    | CF |

Рис. 2.5 Флаги процессора 8086

Флаги TF, IF, DF относятся к управляющим флагам, остальные - к условным (флагам состояния). Флаги отражают следующие условия:

- флаг переноса *CF* устанавливается в 1 при переносе/заеме, возникающем при сложении/вычитании байтов или слов, а также принимает значение выдвигаемого бита при сдвигах операнда;

- флаг четности РГ устанавливается в 1, если младшие 8 бит резуль-

тата имеют четное число единиц;

- флаг вспомогательного переноса AF устанавливается в 1, если есть перенос/заем из младшей тетрады в старшую 8- или 16-битного результата в операциях десятичного сложения/вычитания;

- флаг нуля ZF устанавливается в 1 при нулевом результате операции;

- флаг знака *SF* устанавливается в 1 при отрицательном результате операции при использовании дополнительного кода;

- флаг переполнения *OF* устанавливается в 1 при потере старшего бита результата сложения или вычитания;

- если флаг направления DF установлен в 1, то используется автодекрементная адресация при выполнении операции обработки строк, если DF установлен в 0, то используется автоинкрементная адресация;

- если флаг прерывания *IF* установлен в 1, то внешние маскируемые прерывания разрешены, иначе запрещены;

- если флаг трассировки TF установлен в 1, то процессор переходит в состояние прерывания после выполнения каждой операции, что позволяет проводить пошаговую отладку программ.

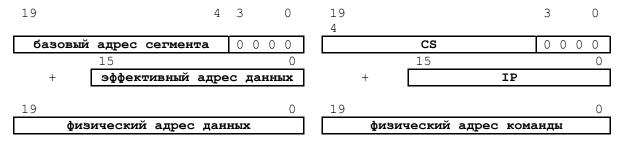

### 2.2.3 Организация памяти

Хотя процессор имеет 20-разрядную адресную шину, которая соединяет его с физической памятью, он оперирует с 16-битными логическими адресами, состоящими из 16-разрядного базового адреса сегмента и 16разрядного смещения в сегменте. Физические, 20-разрядные адреса данных и команд формируются путем сложения содержимого регистровуказателей и смещенного на 4 бита влево содержимого сегментных регистров. Т.н. эффективный адрес данных получается как сумма содержимого регистров ВХ или ВР, содержимого регистров SI или DI и смещения. Затем из эффективного адреса и содержимого сегментного регистра формируется физический адрес (Рис. 2.6). В формировании физического адреса команды участвуют IP и CS. Таким образом, адресное пространство разбивается на 4 сегмента емкостью 64К адресов по числу сегментных регистров. Регистр CS указывает на текущий сегмент кода (программы), откуда выбираются команды. Регистр DS указывает на текущий сегмент данных, в котором содержатся переменные. Регистр SS адресует текущий сегмент стека, в котором реализуются все стековые операции. Наконец, регистр ES определяет текущий дополнительный сегмент данных. Смещенное содержимое сегментного регистра определяет положение сегмента в 20-разрядном адресном пространстве, а регистры-указатели определяют положение команды или данных внутри сегментов.

Поскольку при формировании эффективного адреса содержимое сегментного регистра сдвигается на 4 бита, сегмент всегда начинается с адре-

са, кратного 16, т.е. на границе 16-байтового блока памяти (параграфа). Сегменты в памяти могут располагаться как последовательно, так и с наложением друг на друга. Если программа превышает 64 Кбайт, то необходимо перезагружать сегментный регистр СS новым значением базового адреса. Точно также, если данные превышают 64 Кбайт, то необходимо перезагрузить регистр DS.

Рис. 2.6 Формирование физического адреса данных и команды

Память организована в виде одномерного массива байтов с физическими адресами от  $00000_{16}$  до FFFFF<sub>16</sub>. Две области адресного пространства памяти зарезервированы для выполнения специальных функций, связанных с обработкой прерываний и системным сбросом. Этими областями являются первые 128 байт (физические адреса 00000 - 0007F) и последние 16 байт (физические адреса FFFFO - FFFFF). Данные области использовать для других целей нельзя.

Байты в памяти организуются в слова таким образом, что байту, имеющему меньший адрес, соответствуют менее значимые позиции разрядов в слове. Каждый байт или слово памяти адресуется с помощью 20-битного адреса, причем в случае адресации слова адрес указывает на его младшую часть. Например, адрес  $00000_{16}$  может обозначать и байт с этим адресом, что условно записывается в виде [00000] = 34h, и слово с таким же адресом, что записывается в виде [00000] = 1234h. Тогда старший байт слова, [00001] = 12h. Квадратные скобки обозначают ячейку памяти, адрес которой находится в этих скобках, h – шестнадцатеричную систему счисления. Команды, байты и слова можно размещать по любому адресу байта, однако рекомендуется размещать слова в памяти по четным адресам, так как процессор может передавать такие слова за один цикл обращения к памяти. Слово с четным адресом называется выравненным на границу слова. Слова с нечетными адресами (невыравненные) также допустимы, однако они считываются в два раза медленнее (требуют два цикла обращения к памяти).

### 2.2.4 Форматы команд

Команды i8086 имеют переменную длину от 1 до 6 байт. По числу обрабатываемых операндов команды подразделяются на безадресные, одноадресные и двухадресные. В двухадресных командах результат всегда записывается по первому адресу и только один из операндов может находиться в памяти. При этом в мнемонике, операнд-приемник записывается слева от запятой-разделителя операндов, а операнд-источник — справа.

Всего существует четыре источника операндов: тело команды, регистр, память и порт ввода/вывода. В первом случае операнд называется непосредственным.

Первый байт команды содержит код операции ( $KO\Pi$ ), в состав которого могут входить специальные разряды d, s и w. При w=1 операции выполняются с 16-разрядными словами, при w=0 – с байтами. Разряд d определяет направление передачи данных в двухоперандных командах: из регистра в регистр/память (d=0) или из регистра/памяти в регистр (d=1). S – определяет расширение 8-битных непосредственных данных до полного размера (s=1) или нет (s=0). При некоторых сочетаниях команд и методов адресации (регистровый метод адресации) положение операнда может задаваться непосредственно в байте кода операции (см. следующий раздел), но чаще для этого используется т.н. «постбайт».

В командах, имеющих длину 2 и более байта, второй байт называется *постбайтом*. Он выполняет функции кодирования адресов операндов. Байты 3 - 6 присутствуют в команде в зависимости от типа адреса операнда, описанного постбайтом и наличия непосредственного операнда.

Постбайт состоит из трех полей: *режима - MOD*, *регистра - REG* и *регистра/памяти - R/M*. Поле MOD занимает 2 бита (6 и 7) постбайта. Поле REG занимает 3 бита (3-5) постбайта. Поле R/M занимает 3 бита (0-2) постбайта. Полями MOD и R/M совместно кодируется тип адреса операнда, находящегося в памяти или регистре. 32 значения этих полей определяют нахождение операнда 24 возможными методами адресации либо в одном из 8 регистров.

Ниже приведена структура байта кода операции и постбайта, а в таблицах показано формирование адресов регистровых операндов и адресов операндов памяти. DISP8 и DISP16 — смещения длиной 8 и 16 бит, расположенные в команде непосредственно за байтом адресации.

|   | КОП |     |   |    |    | П  | стб  | айт | 7  |     |

|---|-----|-----|---|----|----|----|------|-----|----|-----|

| 7 |     | 1   | 0 | 7  | 6  | 5  | 4    | 3   | 2  | 1 0 |

|   |     | S/D | W | M( | OD | RE | EG/( | ЭC  | R/ | /M  |

Рис. 2.7 Формат байта КОП и постбайта

| Таблица 2 Фо | рмат поля | <b>REG</b> |

|--------------|-----------|------------|

|--------------|-----------|------------|

| Поле | Регистры |     | Carmananananana     |

|------|----------|-----|---------------------|

| REG  | W=1      | W=0 | Сегментные регистры |

| 000  | AX       | AL  | ES                  |

| 001  | CX       | CL  | CS                  |

| 010  | DX       | DL  | SS                  |

| 011  | BX       | BL  | DS                  |

| 100  | SP       | AH  | -                   |

| 101 | BP | СН | - |

|-----|----|----|---|

| 110 | SI | DH | - |

| 111 | DI | ВН | - |

Таблица 3 Кодирование типа адреса операнда

| Поле | Поле | Базовый | Эффективный    | Длина   |

|------|------|---------|----------------|---------|

| MOD  | R/M  | регистр | адрес          | команды |

| 00   | 000  | DS      | [BX+SI]        | 2       |

| 00   | 001  | DS      | [BX+DI]        | 2       |

| 00   | 010  | SS      | [BP+SI]        | 2       |

| 00   | 011  | SS      | [BP+DI]        | 2       |

| 00   | 100  | DS      | [SI]           | 2       |

| 00   | 101  | DS      | [DI]           | 2       |

| 00   | 110  | DS      | DISP16         | 4       |

| 00   | 111  | DS      | [BX]           | 2       |

| 01   | 000  | DS      | DISP8+[BX+SI]  | 3       |

| 01   | 001  | DS      | DISP8+[BX+DI]  | 3       |

| 01   | 010  | SS      | DISP8+[BP+SI]  | 3       |

| 01   | 011  | SS      | DISP8+[DP+DI]  | 3       |

| 01   | 100  | DS      | DISP8+[SI]     | 3       |

| 01   | 101  | DS      | DISP8+[DI]     | 3       |

| 01   | 110  | SS      | DISP8+[BP]     | 3       |

| 01   | 111  | DS      | DISP8+[BX]     | 3       |

| 10   | 000  | DS      | DISP16+[BX+SI] | 4       |

| 10   | 001  | DS      | DISP16+[BX+DI] | 4       |

| 10   | 010  | SS      | DISP16+[BP+SI] | 4       |

| 10   | 011  | SS      | DISP16+[BP+DI] | 4       |

| 10   | 100  | DS      | DISP16+[SI]    | 4       |

| 10   | 101  | DS      | DISP16+[DI]    | 4       |

| 10   | 110  | SS      | DISP16+[BP]    | 4       |

| 10   | 111  | DS      | DISP16+[BX]    | 4       |

| 11   | 000  | -       | AX or AL       | 2       |

| 11   | 001  | -       | CX or CL       | 2       |

| 11   | 010  | -       | DX or DL       | 2       |

| 11   | 011  | -       | BX or BL       | 2       |

| 11   | 100  | -       | SP or AH       | 2       |

| 11   | 101  | -       | BP or CH       | 2       |

| 11   | 110  | -       | SI or DH       | 2       |

| 11   | 111  | -       | DI or BH       | 2       |

Команде может предшествовать префикс — байт со специальным кодированием, которое изменяет операцию следующей за ним команды. В системе команд процессоров 8086/8088 есть два таких префикса — REP (RE-

Peat) для повторения команд обработки строк и SEG (SEGment) для прямого указания команде сегментного регистра вместо регистра, используемого по умолчанию.

### 2.2.5 Методы адресации

Методы адресации можно разделить на два класса: адресация данных и адресация переходов. Все методы можно отнести к одной из следующих групп:

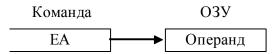

### Прямая адресация.

16-битный эффективный адрес (EA) операнда является частью команды:

### Пример: mov al, [0000h]

| Код           | Действие                                         |

|---------------|--------------------------------------------------|

| a00000        | Запись байта с адресом 0000h в регистр al        |

| До выполнения | После выполнения                                 |

| al=0          | al=7                                             |

| [0000]=7      | [0000]=7 (Предварительно запишите 7 в DS:[0000]) |

| ip=100        | ip=103                                           |

Примечание: запись в квадратных скобках обозначает ячейку, адрес которой (смещение по отношению к DS) записан в квадратных скобках.

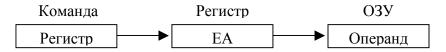

### Регистровая адресация.

Операнд содержится в определяемом командой регистре. 16-битный операнд может находиться в регистрах AX, BX, CX, DX, SI, DI, SP или BP, а 8-битный - в регистрах AH, AL, BH, BL, CH, CL, DH, DL:

| Команда | Регистр     |

|---------|-------------|

| Регистр | <br>Операнд |

### Пример: mov ax, bx

| Код           | Действие                                     |  |

|---------------|----------------------------------------------|--|

| 8bc3          | Запись содержимого регистра bx, в регистр ах |  |

| До выполнения | После выполнения                             |  |

| ax=7          | ax=3                                         |  |

| bx=3          | bx=3                                         |  |

| ip=100        | ip=102                                       |  |

### Косвенно-регистровая адресация.

Эффективный адрес операнда находится в базовом регистре BX или индексном регистре (SI или DI):

## Пример: mov ax, [bx]

| Действие |

|----------|

|          |

| 8b07 | Запись содержимого ячейки памяти с адресом из регистра bx (смещение внутри сегмента DS), в ре- |

|------|------------------------------------------------------------------------------------------------|

|      | гистр ах                                                                                       |

### До выполнения

#### После выполнения

| ax=3     | ax=7                                             |

|----------|--------------------------------------------------|

| bx=0     | bx=0                                             |

| [0000]=7 | [0000]=7 (Предварительно запишите 7 в DS:[0000]) |

| ip=100   | ip=102                                           |

Физический адрес определяется парой сегмент-смещение (например CS:IP — адрес следующей команды), и для каждого регистра, содержащего смещение, есть сегментный регистр, заданный по умолчанию. Некоторые сегменты разрешается принудительно переназначать, мнемоническое обозначение переназначения — «сегментный\_регистр:смещение», в коде команды появляется дополнительный (первый) байт — байт замены сегмента.

| Регистры, хранящие смеще-      | Сегмент «по умолча- | Возможная  |

|--------------------------------|---------------------|------------|

| ние                            | НИЮ≫                | замена     |

| IP                             | CS                  | -          |

| SP                             | SS                  | -          |

| BP                             | SS                  | CS, DS, ES |

| BP+SI, BP+DI                   | SS                  | CS, DS, ES |

| BX                             | DS                  | CS, DS, ES |

| SI, DI (кроме адресации строк) | DS                  | CS, DS, ES |

| SI (адресация строк)           | DS                  | CS, DS, ES |

| DI (адресация строк)           | ES                  | -          |

## Пример: mov ax, cs:[bx]

Код Действие

| 2e8b07 | Запись содержимого ячейки памяти с адресом из регистра bx (смещение внутри сегмента CS), в ре- |

|--------|------------------------------------------------------------------------------------------------|

|        | гистр ах                                                                                       |

#### До выполнения

#### После выполнения

| ax=3         | ax=5                                              |

|--------------|---------------------------------------------------|

| bx=103       | bx=103                                            |

| cs=1554      | cs=1554 (посмотрите на текущее значение CS у Bac) |

| [1554:103]=5 | [1554:103]=5 (предварительно запишите [103]=5)    |

| ip=100       | ip=103                                            |

### Непосредственная адресация.

Операнд длиной байт или слово является частью команды. Операнд помещается в последние байты команды, причем младший байт следует первым (находится по меньшему адресу).

| Команда |  |

|---------|--|

| Операнд |  |

### Пример: mov ax, 1234h

Код Действие

| b83412 | Запись операнда, указанного в команде, в регистр |

|--------|--------------------------------------------------|

| 005412 | ax                                               |

### До выполнения

### После выполнения

| ax=5   | ax=1234 |

|--------|---------|

| ip=100 | ip=103  |

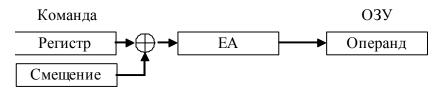

## Относительная косвенно-регистровая адресация.

Эффективный адрес операнда – сумма 8- или 16-разрядного смещения и значения одного из базовых или индексных регистров. Этот метод также называют *базовым*, если используются регистры BX, BP или *индексным*, при использовании SI, DI.

Базовая адресация обеспечивает возможность работы со структурами

данных, размещенными в памяти, например, с соседними ячейками памяти относительно эффективного адреса в базовом регистре.

## Пример: mov ax, [bx+10], другая форма записи - mov ax, 10[bx]

| Код | Действие |

|-----|----------|

|     |          |

| 8b4710 | Запись содержимого ячейки памяти с EA (сегмент DS), определяемым как сумма содержимого bx и |

|--------|---------------------------------------------------------------------------------------------|

|        | смещения в команде (100+10=110) в регистр ах                                                |

### До выполнения

### После выполнения

| ax=1234 | ax=4                                            |

|---------|-------------------------------------------------|

| bx=100  | bx=100                                          |

| [110]=4 | [110]=4 (Предварительно запишите 4 в DS:[0110]) |

| ip=100  | ip=103                                          |

Индексный метод адресации удобен при обработке массивов, когда смещение указывает стартовый адрес массива, а содержимое индексного регистра соответствует индексу массива.

## Пример: mov ax, 0100[si], другая форма записи - mov ax, [si+0100]

Код Действие

| 8b840001 | Запись содержимого ячейки памяти с EA (сегмент DS), определяемым как сумма содержимого si и смещения в команде (2+100=102) в регистр ах. Можно рассматривать значение si как индекс массива со стартовым адресом 100. |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

### До выполнения

#### После выполнения

| ax=4321  | ax=7                                             |

|----------|--------------------------------------------------|

| si=2     | si=2                                             |

| [0102]=7 | [0102]=7 (Предварительно запишите 7 в DS:[0102]) |

| ip=100   | ip=104                                           |

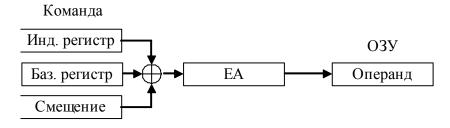

## Базовая индексная адресация.

Эффективный адрес равен сумме содержимого базового (BX или BP) и индексного (SI или DI) регистров.

### Пример: mov ax, 100[bx][si], другая форма записи - mov ax, [bx+si+0100]

| Код      | Действие                                                                                                                                                                                                                                                                                       |  |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 8b800001 | Запись содержимого ячейки памяти с EA (сегмент DS), определяемым как сумма содержимого регистров si, bx и смещения в команде (10+2+100=112) в регистр ах. Можно рассматривать значение si как индекс выбранного регистром bx одномерного массива в двумерном массиве со стартовым адресом 100. |  |

| До выполнения | После выполнения                                 |

|---------------|--------------------------------------------------|

| ax=7          | ax=5                                             |

| bx=10         | bx=10                                            |

| si=2          | si=2                                             |

| [0112]=5      | [0112]=5 (Предварительно запишите 5 в DS:[0112]) |

| ip=100        | ip=104                                           |

### Неявная адресация.

Неявная адресация задается операцией. Например, в командах обработки строк неявно используются регистры SI, DI. В командах управления циклами неявно используется регистр СХ и т.д.

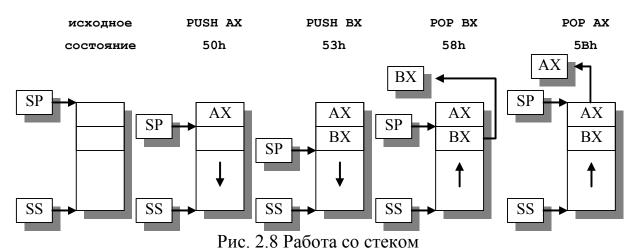

### Стековая адресация.

Стековая адресация применяется в командах работы со стеком PUSH и POP. Для этих команд адрес операнда находится в указателе стека SP и автоматически уменьшается или увеличивается на два при записи в стек или при чтении из стека. Заполнение стека происходит в направлении уменьшения адресов ячеек памяти. Стек может обмениваться данными с регистрами общего назначения и сегментными регистрами. Команды обмена данными между стеком и памятью содержат байт адресации, в котором 3-разрядное поле REG, совместно с полем КОП, идентифицирует команду.

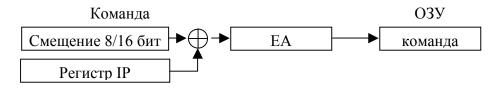

### Адресация переходов. Внутрисегментный прямой переход.

Адрес следующей команды определяется суммированием смещения со знаком, представленным в двоично-дополнительном коде, и значения IP:

## Пример: јтр 100

### Адресация переходов. Внутрисегментный косвенный переход.

Содержимое регистра IP заменяется содержимым регистра или слова памяти, заданным любым методом адресации, кроме непосредственного:

### Пример: jmp [bx]

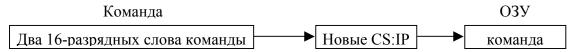

### Адресация переходов. Межсегментный прямой переход.

Содержимое регистров CS и IP заменяются словами из команды:

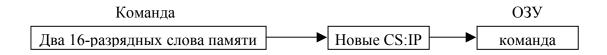

## Адресация переходов. Межсегментный косвенный переход.

Содержимое регистров CS и IP заменяется словами, последовательно расположенными в памяти. Слова могут быть указаны любым методом адресации, кроме непосредственного:

### 2.2.6 Система команд

### Команды передачи данных

предназначены для пересылок данных между регистрами и памятью. Эту группу команд можно разделить на четыре подгруппы: команды пересылки данных общего назначения; команды, использующие аккумулятор; команды пересылки адресных объектов; команды пересылки флагов. Все команды этой группы не влияют на установку флагов, за исключением команд SAHF и POPF.

## Пример: mov ax, bx

## Код Действие

| 8bc3 | Пересылка 16-разрядного содержимого регистра bx |

|------|-------------------------------------------------|

| 0000 | B ax.                                           |

## До выполнения

## После выполнения

| ax=0    | ax=1234 |

|---------|---------|

| bx=1234 | bx=1234 |

| ip=100  | ip=102  |

| Мне-<br>моника | Действие                                                                                           | Байт<br>КОП | Постбайт      |

|----------------|----------------------------------------------------------------------------------------------------|-------------|---------------|

|                | Передача операнда из памяти/операнда регистра в регистр или из регистра в память/операнд регистра. | 100010dw    | mod reg r/m   |

|                | Передача непосредственного операнда в память/операнд регистра.                                     | 1100011w    | mod 000 r/m   |

|                | Передача непосредственного операнда в регистр.                                                     | 1011w reg   | нет           |

| MOV            | Передача операнда из памяти в аккумулятор.                                                         | 1010000w    | нет           |

|                | Передача операнда из аккумулятора в память.                                                        | 1010001w    | нет           |

|                | Передача операнда из памяти/регистра в сегментный регистр.                                         | 10001110    | mod 0 reg r/m |

|                | Передача операнда из сегментного регистра в память/регистр.                                        | 10001100    | mod 0 reg r/m |

| XCHG           | Обмен операндом из памяти/регистра с операндом из регистра.                                        | 1000011w    | mod reg r/m   |

| Acrid          | Обмен операндом из регистра с операндом из аккумулятора.                                           | 10010reg    | нет           |

| PUSH           | Передача операнда из памяти/операнда регистра по адресу в указателе стека SP.                      | 11111111    | mod 110 r/m   |

|                | Передача операнда из регистра по адресу в указателе стека SP.                                      | 01010reg    | нет           |

|                | Передача операнда из сегментного регистра по адресу в указателе стека SP.                          | 000reg110   | нет           |

| POP            | Передача операнда из адреса в указателе стека SP в память/регистр.                                 | 10001111    | mod 000 r/m   |

|       | Передача операнда из адреса в указателе стека SP в регистр.                                                                          | 01011reg | нет         |

|-------|--------------------------------------------------------------------------------------------------------------------------------------|----------|-------------|

|       | Передача операнда из адреса в указателе стека SP в сегментный регистр.                                                               | 000reg11 | нет         |

| PUSHF | Передача содержимого регистра флагов по адресу в указателе стека SP.                                                                 | 10011100 | нет         |

| POPF  | Передача содержимого из адреса в указателе стека SP в регистр флагов.                                                                | 10011101 | нет         |

| LEA   | Загрузка исполнительного адреса памяти в регистр общего назначения.                                                                  | 10001101 | mod reg r/m |

| LDS   | Загрузка из памяти относительного адреса (смещения) и адреса сегмента в один из регистров общего назначения и сегментный регистр DS. | 11000101 | mod reg r/m |

| LES   | Загрузка из памяти относительного адреса (смещения) и адреса сегмента в один из регистров общего назначения и сегментный регистр ES. | 11000100 | mod reg r/m |

| LAHF  | Передача младшего байта регистра флагов в регистр АН.                                                                                | 10011111 | нет         |

| SAHF  | Передача содержимого регистра АН на место младшего байта регистра флагов.                                                            | 10011110 | нет         |

| XLAT  | Передача байта в регистр AL из 256-<br>байтовой таблицы кодов.                                                                       | 11010111 | нет         |

| IN    | Передача байта/слова из фиксированного порта ввода в аккумулятор AL/AX.                                                              | 1110010w | нет         |

| 111   | Передача байта/слова из переменного порта ввода в аккумулятор AL/AX.                                                                 | 1110110w | нет         |

### Арифметические команды

предназначены для выполнения четырех основных видов арифметических действий над 8- и 16- разрядными операндами в знаковом и беззнаковом представлении. Кроме основных арифметических команд имеются операции коррекции арифметических результатов для их перевода в упакованную или неупакованную форму. Признаки полученного результата отображаются в 6 битах регистра Flags (CF, AF, SF, ZF, PF и OF).

## Пример: add ax, bx

| Код | Действие |

|-----|----------|

|-----|----------|

| 03c3 | Сложение 16-разрядного содержимого регистров |

|------|----------------------------------------------|

|      | bx, ах и запись результата в ах.             |

## До выполнения

## После выполнения

| ax=2   | ax=5   |

|--------|--------|

| bx=3   | bx=3   |

| ip=100 | ip=102 |

| Мнемо-<br>ника | Действие                                                                                             | Байт<br>КОП | Постбайт    |

|----------------|------------------------------------------------------------------------------------------------------|-------------|-------------|

|                | Сложение операнда из памяти/регистра с операндом из регистра.                                        | 000000dw    | mod reg r/m |

| ADD            | Сложение непосредственного операнда с операндом из памяти/регистра.                                  | 100000sw    | mod 000 r/m |

|                | Сложение непосредственного операнда с операндом в аккумуляторе.                                      | 0000010w    | нет         |

|                | Сложение операнда из памяти/регистра с операндом из регистра (с учетом переноса).                    | 0001010w    | mod reg r/m |

| ADC            | Сложение непосредственного операнда с операндом из памяти/регистра (с учетом переноса).              | 100000sw    | mod 010 r/m |

|                | Сложение непосредственного операнда с операндом в аккумуляторе (с учетом переноса).                  | 0001010w    | нет         |

| INC            | Увеличение на единицу содержимого памяти/регистра.                                                   | 1111111w    | mod 000 r/m |

| nve            | Увеличение на единицу содержимого регистра.                                                          | 01000reg    | нет         |

| AAA            | Коррекция содержимого аккумулятора AL при сложении двоично-десятичных кодов в неупакованном формате. | 00110111    | нет         |

| DAA            | Тоже, но в упакованном формате.                                                                      | 00100111    | нет         |

| SUB            | Вычисление разности между операндом из памяти/регистра и операндом из регистра.                      | 001010dw    | mod reg r/m |

|                | Вычитание непосредственного операнда из операнда в памяти/регистре.                                  | 100000sw    | mod 101 r/m |

|                | Вычитание непосредственного операнда из операнда в аккумуляторе.                                     | 0010110w    | нет         |

| SBB            | Вычисление разности между операндом из памяти/регистра и операндом из регистра (с заемом).           | 000110dw    | mod reg r/m |

|      | Вычитание непосредственного операнда из операнда в памяти/регистре (с заемом).                            | 100000sw | mod 011 r/m |

|------|-----------------------------------------------------------------------------------------------------------|----------|-------------|

|      | Вычитание непосредственного операнда из операнда в аккумуляторе (с заемом).                               | 0001110w | нет         |

| DEC  | Вычитание единицы из операнда в памяти/регистре.                                                          | 1111111w | mod 001 r/m |

| DLC  | Вычитание единицы из операнда в регистре.                                                                 | 01001reg | нет         |

| NEG  | Вычитание исходного операнда из нуля (изменение знака).                                                   | 1111011w | mod 011 r/m |

|      | Сравнение операнда из памя-ти/регистра с операндом из регистра.                                           | 001110dw | mod 011 r/m |

| CMP  | Сравнение непосредственного операнда с операндом в памяти/регистре.                                       | 100000sw | mod reg r/m |

|      | Сравнение непосредственного операнда с операндом в аккумуляторе.                                          | 0011110w | нет         |

| AAS  | Коррекция содержимого аккумулятора AL при вычитании двоично-десятичных кодов в неупакованном формате.     | 00111111 | нет         |

| DAS  | То же, но в упакованном формате.                                                                          | 00101111 | нет         |

| MUL  | Умножение без учета знака операнда в аккумуляторе на операнд из памяти/регистра.                          |          | mod 100 r/m |

| IMUL | Умножение со знаком операнда из па-<br>мяти/регистра.                                                     | 1111011w | mod 101 r/m |

| DIV  | Деление без учета знака операнда длиной в одно/два слова на операнд из памяти/регистра.                   | 1111011w | mod 110 r/m |

| IDIV | Деление со знаком операнда длиной в одно/два слова на операнд из памя-ти/регистра.                        | 1111011w | mod 111 r/m |

| AAM  | Коррекция содержимого аккумулятора АХ при умножении двоично-<br>десятичных кодов в неупакованном формате. | 11010100 | 00001010    |

| AAD  | Коррекция содержимого аккумулятора AL при делении двоично-десятичных кодов в неупакованном формате.       | 11010101 | 00001010    |

### Логические команды

предназначены для выполнения четырех логических действий над 8- и 16-битовыми логическими структурами: получение инверсного кода, логическое произведение, логическая сумма, сумма по модулю два. Команды AND, TEST, OR и XOR воздействуют на арифметические флаги следующим образом: флаги OF и CF всегда сбрасываются в нулевое состояние; состояния флагов SF, ZF, PF зависят от полученного результата и определяются по тем же правилам, что и в командах арифметических операций; состояние флага AF не определено. Команда NOT не влияет на состояние флагов.

### Пример: not ax

| Действие |

|----------|

|          |

| F7D0 | Значения 16 бит регистра ах меняются на противо- |

|------|--------------------------------------------------|

|      | положные.                                        |

### До выполнения

### После выполнения

| ax=5555 | ax=AAAA |

|---------|---------|

| ip=100  | ip=102  |

| Мнемо-<br>ника | Действие                                                                                                                              | Байт<br>КОП | Постбайт    |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------|-------------|-------------|

| NOT            | Инвертирование разрядов операнда в памяти/регистре.                                                                                   | 1111011w    | mod 010 r/m |

|                | Логическое умножение операнда из памяти/регистра и операнда из регистра.                                                              | 001000dw    | mod reg r/m |

| AND            | Логическое умножение непосредственного операнда и операнда из памяти/регистра.                                                        | 1000000w    | mod 100 r/m |

|                | Логическое умножение непосредственного операнда и операнда в аккумуляторе.                                                            | 0010010w    | нет         |

| TEST           | Установка регистра FLAGS в соответствии с результатом логического умножения операнда из памяти/регистра и операнда из регистра.       | 1000010w    | mod reg r/m |

|                | Установка регистра FLAGS в соответствии с результатом логического умножения непосредственного операнда и операнда из памяти/регистра. | 1111011w    | mod 000 r/m |

|     | Установка регистра FLAGS в соответствии с результатом логического умножения непосредственного операнда и операнда в аккумуляторе. | 1010100w      | нет         |

|-----|-----------------------------------------------------------------------------------------------------------------------------------|---------------|-------------|

|     | Логическое сложение операнда из памяти/регистра и операнда из регистра.                                                           | 000010dw      | mod reg r/m |

| OR  | Логическое сложение непосредственного операнда и операнда из памяти/регистра.                                                     | -<br>1000000w | mod 001 r/m |

|     | Логическое сложение непосредственного операнда и операнда в аккумуляторе.                                                         | 0000110w      | нет         |

|     | Операция "исключающее ИЛИ" над операндами из памяти/регистра и из регистра.                                                       | 001100dw      | mod reg r/m |

| XOR | Операция "исключающее ИЛИ" над непосредственным операндом и операндом из памяти/регистра.                                         | 1000000w      | mod 110 r/m |

|     | Операция "исключающее ИЛИ" над непосредственным операндом и операндом в аккумуляторе.                                             | 0011010w      | нет         |

#### Команды сдвига

предназначены для выполнения логических, арифметических и циклических сдвигов. Поле операнда имеет формат mem/reg, count. Здесь mem/reg адресует регистр или ячейку памяти, а count (счет или счетчик) определяет число сдвигов. Число сдвигов может быть указано как константа 1 (статический сдвиг) или как регистр СL. В первом случае осуществляется сдвиг на один байт, а во втором - число сдвигов определяется содержимым регистра СL, которое должно быть беззнаковым целым двочиным числом. Таким образом, число сдвигов можно задать переменной, вычисляемой во время выполнения программы (так называемый динамический сдвиг). При выполнении команд сдвигов флаги изменяются следующим образом:

- состояние флага АF всегда не определено;

- флаг СF всегда содержит значение последнего выдвинутого бита;

- в однобитных сдвигах флаг OF=0, если операция изменила значение старшего (знакового) бита операнда; при сдвиге на несколько бит состояние флага OF не определено;

- циклические сдвиги влияют только на флаги OF и CF;

- в арифметических и логических сдвигах флаги SF, ZF и PF изменяются в соответствии с полученным результатом.

## Пример: shl ax, 1

| Код | Действие |

|-----|----------|

| тод | Депствис |

|      | Поразрядный сдвиг 16-разрядного содержимого ре-  |

|------|--------------------------------------------------|

| D1E0 | гистра ах на одну двоичную позицию влево, в сто- |

|      | рону старших разрядов.                           |

### До выполнения

### После выполнения

| ax=1111 | ax=2222 |

|---------|---------|

| ip=100  | ip=102  |

| Мнемо-<br>ника | Действие                                                                                                                      | Байт<br>КОП | Постбайт    |

|----------------|-------------------------------------------------------------------------------------------------------------------------------|-------------|-------------|

| SHL,<br>SAL    | Логический (арифметический) сдвиг влево операнда из памяти/регистра на число разрядов, определяемое константой сдвига.        | 110100vw    | mod 100 r/m |

| SHR            | Логический сдвиг вправо операнда из памяти/регистра на число разрядов, определяемое константой сдвига.                        | 110100vw    | mod 101 r/m |

| SAR            | Арифметический сдвиг вправо операнда из памяти/регистра на число разрядов, определяемое константой сдвига.                    | 110100vw    | mod 111 r/m |

| ROL            | Циклический сдвиг влево операнда из памяти/регистра на число разрядов, определяемое константой сдвига.                        | 110100vw    | mod 000 r/m |

| ROR            | Циклический сдвиг вправо операнда из памяти/регистра на число разрядов, определяемое константой сдвига.                       | 110100vw    | mod 001 r/m |

| RCL            | Циклический сдвиг влево, с использованием СF, операнда из памяти/регистра на число разрядов, определяемое константой сдвига.  | 110100vw    | mod 010 r/m |

| RCR            | Циклический сдвиг вправо, с использованием СF, операнда из памяти/регистра на число разрядов, определяемое константой сдвига. | 110100vw    | mod 011 r/m |

### Команды передачи управления

включают в себя безусловные переходы, команды обращения к подпрограммам и возврата из них, а также команды управления циклами. Выполнение этих команд приводит к изменению содержимого указателя команд IP и регистра CS. Команды безусловных переходов и обращений к подпро-

граммам обеспечивают как внутрисегментные, так и межсегментные переходы с прямой и косвенной адресацией. Команды управления циклами обеспечивают переход только в области текущего сегмента с коротким смещением.

## Пример: јтр 110

| Действие |

|----------|

|          |

| EB0E | Загрузка регистра IP значением 110. Следующая |

|------|-----------------------------------------------|

| EDUL | команда имеет внутрисегментный адрес - 110.   |

| До выполнения | После выполнения |

|---------------|------------------|

| ip=100        | ip=110           |

## Пример: call 110

Код Действие

|         | Выполняется декремент SP на 2, в стек включается   |

|---------|----------------------------------------------------|

| E80D000 | содержимое ІР, а затем, к ІР прибавляется смеще-   |

|         | ние, которое интерпретируется, как знаковое целое. |

### До выполнения

### После выполнения

| ip=100    | ip=110    |  |

|-----------|-----------|--|

| sp=80     | sp=7E     |  |

| [80]=0000 | [80]=0000 |  |

| [7E]=0000 | [7E]=0103 |  |

| Мнемо-<br>ника | Действие                                                                | Байт<br>КОП | Постбайт    |

|----------------|-------------------------------------------------------------------------|-------------|-------------|

|                | Безусловный внутрисегментный переход с прямой адресацией.               | 11101001    | нет         |

|                | Безусловный короткий внутрисегмент-<br>ный переход с прямой адресацией. | 11101011    | нет         |

| JMP            | Безусловный внутрисегментный переход с косвенной адресацией.            | 11111111    | mod 100 r/m |

|                | Безусловный межсегментный переход с прямой адресацией.                  | 11101010    | нет         |

|                | Безусловный межсегментный переход с косвенной адресацией.               | 111111111   | mod 101 r/m |

| CALL           | Внутрисегментный вызов подпрограммы с прямой адресацией.                | 11101000    | нет         |

|                   | Внутрисегментный вызов подпрограммы с косвенной адресацией.                              | 11111111 | mod 010 r/m |

|-------------------|------------------------------------------------------------------------------------------|----------|-------------|

|                   | Межсегментный вызов подпрограммы с прямой адресацией.                                    | 10011010 | нет         |

|                   | Межсегментный вызов подпрограммы с косвенной адресацией.                                 | 11111111 | mod 011 r/m |

|                   | Внутрисегментный возврат из подпрограммы.                                                | 11000011 | нет         |

| RET               | Внутрисегментный возврат из подпрограммы с увеличением содержимого указателя стека SP.   | 11000010 | нет         |

| KEI               | Межсегментный возврат из подпрограммы.                                                   | 11001011 | нет         |

|                   | Межсегментный возврат из подпрограммы с увеличением содержимого указателя стека SP.      | 11001010 | нет         |

| LOOP              | Передача управления, если содержимое регистра СХ не равно нулю.                          | 11100010 | нет         |

| LOOPE,<br>LOOPZ   | Передача управления, если содержимое регистра СХ не равно нулю и флаг ZF установлен в 1. | 11100001 | нет         |

| LOOPNE,<br>LOOPNZ | Передача управления, если содержимое регистра СХ не равно нулю и флаг ZF установлен в 0. | 11100000 | нет         |

| JCXZ              | Передача управления, если содержимое регистра СХ равно нулю.                             | 11100011 | нет         |

## Команды условных переходов

обеспечивают только внутрисегментные переходы.

| Мнемоника | Действие                                               | Байт КОП |

|-----------|--------------------------------------------------------|----------|

| JE, JZ    | Передача управления по равенству/нулю.                 | 01110100 |

| JNE, JNZ  | Передача управления, если не равно/не нуль.            | 01110101 |

| JL, JNGE  | Передача управления, если меньше/не больше и не равно. | 01111100 |

| JLE, JNG  | Передача управления, если меньше или равно/не больше.  | 01111110 |

| JB, JNAE  | Передача управления, если меньше/не больше и не равно. | 01110010 |

| JBE, JNA  | Передача управления, если меньше или равно/не больше.  | 01110110 |

| JP, JPE   | Передача управления при четности.                      | 01111010 |

| JNP, JPO | Передача управления при нечетности.                    | 01111011 |

|----------|--------------------------------------------------------|----------|

| JO       | Передача управления при переполнении.                  | 01110000 |

| JNO      | Передача управления при отсутствии переполнения.       | 01110001 |

| JS       | Передача управления по отрицательному результату.      | 01111000 |

| JNS      | Передача управления по положительному результату.      | 01111001 |

| JG, JNLE | Передача управления, если больше/не меньше и не равно. | 01111111 |

| JGE, JNL | Передача управления, если больше или равно/не меньше.  | 01111101 |

| JA, JNBE | Передача управления, если больше/не меньше и не равно. | 01110111 |

| JAE, JNB | Передача управления, если больше или равно/не меньше.  | 01110011 |

### Команды управления процессором

за исключением ESC являются однобайтовыми и могут быть разделены на две группы: команды, изменяющие содержимое регистра флагов, и команды, предназначенные для работы с внешними устройствами и не воздействующие на флаги.

| Мнемоника | Действие                                            | Байт КОП |

|-----------|-----------------------------------------------------|----------|

| CLC       | Сброс признака переноса.                            | 11111000 |

| CMC       | Инвертирование признака переноса.                   | 11110101 |

| STC       | Установка признака переноса.                        | 11111001 |

| CDL       | Сброс признака направления.                         | 11111100 |

| STD       | Установка признака направления.                     | 11111101 |

| CLI       | Сброс признака разрешения прерывания.               | 11111010 |

| HLT       | Останов.                                            | 11110100 |

| WAIT      | Перевод процессора в состояние ожидания.            | 10011011 |

| ESC       | Выдача кода операции или операнда для сопроцессора. | 11011x   |

| LOCK      | Однобайтный префикс блокировки шины.                | 11110000 |

## Команды обработки строк

Все команды обработки строк символов имеют длину один байт. Бит 0 показывает операцию с байтом (бит 0=0) или словом (бит 0=1).

## Пример: movsw

| Код | Действие |

|-----|----------|

| КОД | Денствис |

|    | Выполняется пересылка слова строки источника      |

|----|---------------------------------------------------|

| A5 | (src), адресуемой регистром SI, в строку приемни- |

| AJ | ка (dst), адресуемую регистром DI. Команда не ус- |

|    | танавливает флагов.                               |

## До выполнения

## После выполнения

| ip=100    | ip=101    |

|-----------|-----------|

| si=20     | si=22     |

| di=50     | di=52     |

| [20]=0102 | [20]=0102 |

| [50]=0000 | [50]=0102 |

## Пример: rep movsw

Код Действие

|      | Выполняется пересылка строки источника (src), ад-                                               |

|------|-------------------------------------------------------------------------------------------------|

|      | ресуемой регистром SI, в строку приемника (dst), адресуемую регистром DI. На каждом шаге произ- |

| F3A5 |                                                                                                 |

|      | водится коррекция индексных регистров на требуе-                                                |

|      | мую величину и направление. Выполнение ко-                                                      |

|      | манды прекращается по исчерпании счетчика СХ.                                                   |

## До выполнения

## После выполнения

| ip=100    | ip=102    |

|-----------|-----------|

| si=20     | si=26     |

| di=50     | di=56     |

| cx=3      | cx=0      |

| [20]=0102 | [20]=0102 |

| [22]=0304 | [22]=0304 |

| [24]=0506 | [24]=0506 |

| [50]=0000 | [50]=0102 |

| [52]=0000 | [52]=0304 |

| [54]=0000 | [54]=0506 |

| Мнемоника       | Действие                                                                                  | Байт КОП |

|-----------------|-------------------------------------------------------------------------------------------|----------|

| KHP             | Циклическое повторение команды обработки<br>строки, количество повторов – в СХ. (Префикс) | 1111001z |

| MOVSB,<br>MOVSW | Передача элемента строки - байта/слова.                                                   | 1010010w |

| CMPSB,<br>CMPSW | Сравнение элементов строк - байтов/слов.                              | 1010011w |

|-----------------|-----------------------------------------------------------------------|----------|

| SCASB,<br>SCASW | Сканирование строк символов - байтов/слов.                            | 1010111w |

| LODSB,<br>LODSW | Загрузка элементов строк символов - бай-<br>тов/слов в регистр AL/AX. | 1010110w |

| STOSB,<br>STOSW | Запись байтов/слов из регистра AL/AX в строку символов.               | 1010101w |

### 2.2.7 Математический сопроцессор

Математический сопроцессор (MCP - math coprocessor) — это расширение основной архитектуры и множества команд основного процессора. Сопроцессор дополняет возможности процессора новыми командами для работы с вещественными числами и новыми регистрами и реализован в виде отдельной ИС для процессоров до 80386 включительно (8087, 80287, 80387), либо непосредственно в микросхеме центрального процессора, как внутренний модуль (Floating Point Unit, FPU). Сопроцессор поддерживает семь типов данных: 16-, 32-, 64-битные целые числа; 32-, 64-, 80-битные вещественные числа и 18-разрядные числа в двоично-десятичном формате. Форматы чисел с плавающей точкой соответствуют стандартам IEEE 754, 854 и представлены на Рис. 2.9, где  $D_i$  — разряды десятичного числа в двоично-десятичном представлении; М — мантисса, Е — порядок вещественного числа, а S — знаковый разряд.

Декодирование инструкций для сопроцессора и доставка данных осуществляется основным процессором, сопроцессор только исполняет свои команды. Для хранения операндов и промежуточных данных имеется восемь 80-разрядных регистров данных R0-R7, в которых данные представлены в расширенном вещественном формате (см. Рис. 2.9). При загрузке регистра из памяти, данные автоматически преобразуются в этот формат. Регистры данных образуют стек, обращение к которому возможно через относительные имена ST(N). Пять регистров специального назначения служат для управления вычислениями и определения состояния сопроцессора (Рис. 2.10).

Слово состояния (SW) состоит из флагов (начиная с 0-го разряда): IE — недействительная команда (пустой операнд, неопределенный результат), DE — денормализован хотя бы один из операндов, ZE — деление на нуль, ОЕ - переполнение, UE - антипереполнение, PE — выполнено округление, ES (другое обозначение - IR) — возникновение немаскируемого исключения, C[0:3] — код условия, интерпретируемый в зависимости от выполненной команды, ST[0:2] (Stack Top) — номер регистра из стека, выполняющего роль вершины стека.

Управляющее слово (CW) - определяет условия выполнения команд. Разряды 0..5 маскируют исключения: IM – неверная команда, DM – операнд денормализован, ZM – деление на нуль, OM - переполнение, U M -

антипереполнение, РМ — округление. Поле РС (биты 8,9) — управление точностью: 00-24 бита, 10-53 бита, 11-64 бита. Поле RC (биты 10,11) — управление округлением:  $00-\kappa$  ближайшему значению,  $01-\kappa$  - $\infty$ ,  $10-\kappa$  + $\infty$ ,  $11-\kappa$  нулю.

Слово мэгов (ТW) - состоит из восьми двухбитных признаков (тэгов) для каждого из регистров данных сопроцессора. Четыре возможных значения тэга: 00, 01, 10, 11, определяют содержимое регистра как, соответственно, ненулевое число, нуль, специальное значение (бесконечность, неизвестный формат, и т.п.)

| Название                      | Диапазон         | <b>I</b> 15 0                     |   |                                                                  |

|-------------------------------|------------------|-----------------------------------|---|------------------------------------------------------------------|

| Целое слово                   | $10^{4}$         | S                                 |   |                                                                  |

| Короткое целое                | 10 <sup>9</sup>  | 31 0<br>S                         |   |                                                                  |

| Длинное целое                 | 10 <sup>19</sup> | 63<br>S                           |   | 0                                                                |

| Упакованное десятичное        | $10^{18}$        | 7978 72 71<br>S X D <sub>17</sub> |   | $\begin{array}{c cccc} & 4 & 3 & 0 \\ & D_1 & D_0 & \end{array}$ |

| Вещественное одинарной точн.  | $10^{\pm 38}$    | 3130 23 22 0<br>S E M             |   |                                                                  |

| Вещественное двойной точности | $10^{\pm 308}$   | 6362 52 51<br>S E                 | M | 0                                                                |

| Расширенное вещественное      | $10^{\pm 4932}$  | 7978 64 63 62<br>S E 1            | M | 0                                                                |

Рис. 2.9 Форматы данных сопроцессора

#### Регистровый стек Регистры специального назначения 64 63 ST(6) R0 Е M Регистр управления ST(7) Rl SWST(0) Регистр состояния R2 вершина стека R3 ST(1) 0 15 TWST(2) Слово тэгов R4 47 R5 ST(3) 0 IP Указатель команды R6 ST(4) 0 R7 ST(5) DP Указатель данных Положение вершины стека определя-10 OC КОП (OpCode) ет поле TOP регистра SW - в его битах 13-11 находится номер одного из Rn регистров.

Рис. 2.10 Регистры сопроцессора

Система команд сопроцессора состоит из команд передачи данных и за-

грузки констант, основных арифметических команд, сравнения, управления сопроцессором. Все команды сопроцессоры относятся к классу т.н. ESC- команд и начинаются с битовой последовательности 11011 (D1 $_{16}$ ). Ниже приведены ассемблерная мнемоника и краткое описание действий команд. Операнды обозначены следующим образом:

- m32real, m64real, m80real вещественные числа в памяти;

- m16int, m32int, m64int целочисленные значения в памяти;

- m80bcd упакованное двоично-десятичное число;

- st(i) регистр стека сопроцессора, смещенный от верхушки на i;

- reg/mem операнд в регистре/памяти.

### Команды передачи данных и загрузки констант

| FLD src    | $st(0) \leftarrow src (m32real/m64real/m80real)$    |

|------------|-----------------------------------------------------|

| FILD src   | $st(0) \leftarrow src (m16int/m32int/m64int)$       |

| FBLD src   | $st(0) \leftarrow src (m80bcd)$                     |

| FLDZ       | $st(0) \leftarrow 0.0$                              |

| FLD1       | $st(0) \leftarrow 1.0$                              |

| FLDPI      | $st(0) \leftarrow \pi$                              |

| FLDL2T     | $st(0) \leftarrow log_2(10)$                        |

| FLDL2E     | $st(0) \leftarrow log_2(e)$                         |

| FLDLG2     | $st(0) \leftarrow \log_{10}(2)$                     |

| FLDLN2     | $st(0) \leftarrow ln(2)$                            |

| FST dest   | $dest \leftarrow st(0) \text{ (m32real/m64real)}$   |

| FSTP dest  | dest ← st(0) (m32real/64/80); "вытолкнуть" стек     |

| FIST dest  | $dest \leftarrow st(0) (m16int/32)$                 |

| FISTP dest | dest ← st(0) (m16int/32/64); "вытолкнуть" стек      |

| FBST dest  | $dest \leftarrow st(0) \text{ (m80bcd)}$            |

| FBSTP dest | $dest \leftarrow st(0) (m80bcd);$ "вытолкнуть" стек |

### Команды сравнения

| FCOM          | Установить флаги как для $st(0)$ - $st(1)$              |

|---------------|---------------------------------------------------------|

| FCOM op       | Установить флаги как для st(0) - op (m32real/64)        |

| FCOMP op      | Сравнить st(0) с ор (reg/m32real/64); "вытолкнуть" стек |

| FCOMPP        | Сравнить $st(0)$ с $st(1)$ ; "вытолкнуть" стек 2 раза   |

| FICOM op      | Установить флаги как для st(0) - op (m16int/m32int)     |

| FICOMP op     | Сравнить st(0) с ор (m16int/m32int); "вытолкнуть" стек  |

| FTST          | Сравнить st(0) с 0.0                                    |

| FXAM          | Установить флаги по содержимому st(0)                   |

| FUCOMP st(i)  | Сравнить $st(0)$ с $st(i)$ ; "вытолкнуть" стек          |

| FUCOMPP st(i) | Сравнить st(0) c st(i); "вытолкнуть" стек 2 раза        |

## Арифметические команды и команды трансцендентных функций

| FADD | $st(0) \leftarrow st(0) + st(1)$ |

|------|----------------------------------|

|------|----------------------------------|

| EADD            | (0) (0) (0) (1) (4 1)                                     |

|-----------------|-----------------------------------------------------------|

| FADD src        | $st(0) \leftarrow st(0) + src (m32real/m64real)$          |

| FADD st(i),st   | $st(i) \leftarrow st(i) + st(0)$                          |

| FADDP st(i),st  | $st(i) \leftarrow st(i) + st(0)$ ; "вытолкнуть" стек      |

| FIADD src       | $st(0) \leftarrow st(0) + src (m16real/m32real)$          |

| FSUB            | $st(0) \leftarrow st(0) - st(1)$                          |

| FSUB src        | $st(0) \leftarrow st(0) - src (reg/mem)$                  |

| FSUB st(i),st   | $st(i) \leftarrow st(i) - st(0)$                          |

| FSUBP st(i),st  | $st(i) \leftarrow st(i)$ - $st(0)$ ; "вытолкнуть" стек    |

| FSUBR st(i),st  | $st(0) \leftarrow st(i) - st(0)$                          |

| FSUBRP st(i),st | $st(0) \leftarrow st(i)$ - $st(0)$ ; "вытолкнуть" стек    |

| FISUB src       | $st(0) \leftarrow st(0) - src (m16int/m32int)$            |

| FISUBR src      | $st(0) \leftarrow src - st(0) (m16int/m32int)$            |

| FMUL            | $st(0) \leftarrow st(0) * st(1)$                          |

| FMUL st(i)      | $st(0) \leftarrow st(0) * st(i)$                          |

| FMUL st(i),st   | $st(i) \leftarrow st(0) * st(i)$                          |

| FMULP st(i),st  | $st(i) \leftarrow st(0) * st(i);$ "вытолкнуть" стек       |

| FIMUL src       | $st(0) \leftarrow st(0) * src (m16int/m32int)$            |

| FDIV            | $st(0) \leftarrow st(0) \div st(1)$                       |

| FDIV st(i)      | $st(0) \leftarrow st(0) \div st(i)$                       |

| FDIV st(i),st   | $st(i) \leftarrow st(0) \div st(i)$                       |

| FDIVP st(i),st  | $st(i) \leftarrow st(0) \div st(i)$ ; "вытолкнуть" стек   |

| FIDIV src       | $st(0) \leftarrow st(0) \div src (m16int/m32int)$         |

| FDIVR st(i),st  | $st(0) \leftarrow st(i) \div st(0)$                       |

| FDIVRP st(i),st | $st(0) \leftarrow st(i) \div st(0)$ ; "вытолкнуть" стек   |

| FIDIVR src      | $st(0) \leftarrow src \div st(0) \text{ (m16int/m32int)}$ |

| FSQRT           | $st(0) \leftarrow$ квадратный корень от $st(0)$           |

| FSCALE          | $st(0) \leftarrow$ масштабировать на степень 2-ки $st(0)$ |

| FXTRACT         | $st(0) \leftarrow$ порядок $st(0)$ ; втолкнуть в стек;    |

|                 | $st(0) \leftarrow \text{мантисса } st(0)$                 |

| FPREM           | $st(0) \leftarrow st(0) \text{ MOD } st(1)$               |

| FRNDINT         | $st(0) \leftarrow INT(st(0))$ ; зависит от флага RC       |

| FABS            | $st(0) \leftarrow ABS(st(0))$ ; убрать знак               |

| FCHS            | $st(0) \leftarrow -st(0)$                                 |

| FCOS            | $st(0) \leftarrow COS(st(0))$                             |

| FPTAN           | $st(0) \leftarrow TAN(st(0))$                             |

| FPATAN          | $st(0) \leftarrow ATAN(st(0))$                            |

| FSIN            | $st(0) \leftarrow SIN(st(0))$                             |

|                 |                                                           |

## Команды управления сопроцессором

| FINIT      | Инициализировать сопроцессор |

|------------|------------------------------|

| FSTSW AX   | $AX \leftarrow MSW$          |

| FSTSW dest | dest ← MSW (m16int)          |

| FLDCW src  | FPU CW ← src (m16int)        |

| FSTCW dest | dest ← FPU CW                |

| FCLEX       | Очистить исключения                                                  |

|-------------|----------------------------------------------------------------------|

| FSTENV dest | записать слова состояния, управления, тэгов и                        |

|             | указатели исключений в память – dest                                 |

| FLDENV src  | загрузить окружение с src                                            |

| FSAVE dest  | записать состояние сопроцессора в 94-байтное dest                    |

| FRSTOR src  | восстановить состояние сопроцессора,                                 |

|             | сохраненное FSAVE                                                    |

| FINCSTP     | $st(6) \leftarrow st(5); st(5) \leftarrow st(4),,st(0) \leftarrow ?$ |

| FDECSTP     | $st(0) \leftarrow st(1); st(1) \leftarrow st(2),,st(7) \leftarrow ?$ |

| FFREE st(i) | Отметить регистр st(i) как неиспользуемый                            |

| FNOP        | $st(0) \leftarrow st(0)$ , холостая команда                          |

| WAIT/FWAIT  | Остановить ЦПУ, пока сопроцессор не завершил                         |

|             | выполнение текущей команды                                           |

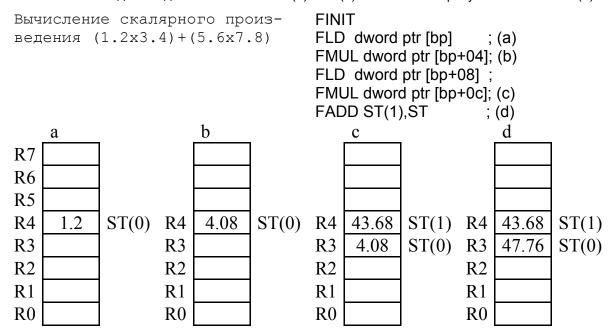

Покажем, как используется стек сопроцессора и его команды для выполнения последовательности вычислений на примере вычисления скалярного произведения (Рис. 2.11). Вначале разместим исходные данные в сегменте данных DS последовательно (1.2; 3.4; 5.6; 7.8) в формате float. Для этого изменим представление данных сегмента DS как данных с плавающей точкой (Ctrl $^D$   $\rightarrow$  Float).

- 1. Перед работой со стеком сопроцессора, выполним сброс FINIT.

- 2. Вторая команда FLD dword ptr [bp] выполняет декремент указателя стека и загружает значение 1.2 из DS:BP в ST(0).

- 3. Третья команда умножает значение ST(0) на операнд 3.4 из DS:[BP+4] и записывает результат в ST(0).

- 4. Четвертая команда выполняет декремент указателя стека и загружает значение 5.6 из памяти DS:[BP+8] в ST(0).

- 5. Пятая команда умножает значение ST(0) на значение 7.8 из DS:[BP+0C] и записывает результат в ST(0).

- 6. Шестая команда складывает значения ST(1) и ST(0) и записывает результат 47.76 в ST(0).